你是否在为在仿真中无法给数字模块打入码字而苦恼?

你是否在因 Modelsim 导出波形的繁琐而感到心烦?

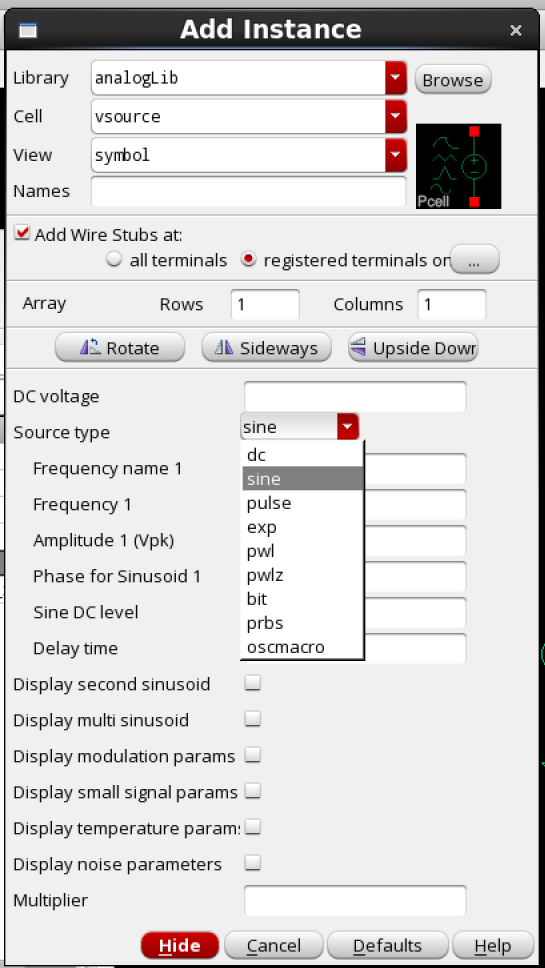

那么,调用 analogLib 库中的 vsource 即可满足你的需求!

上图就是 vsource 的属性框,其中 Source type 包括了许多 vsource 可用的类型。我们要使用的是其中的 bit 类型。

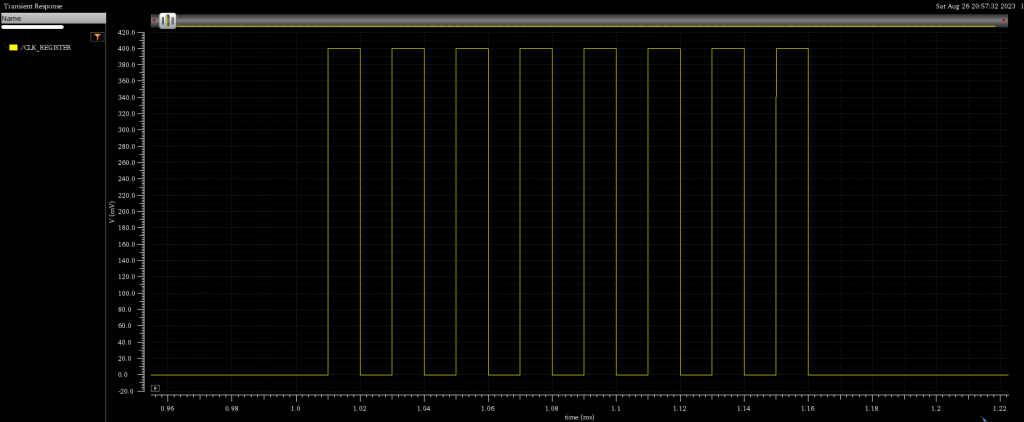

实例1 – 产生 8 个周期的 Clock 信号

有时,我们需要产生一小段 Clock 信号,来将码字输入到数字模块中。在数据输入完成后,我们便不希望再有多余的 Clock 信号产生。

这个需求如果想要通过 vpulse 产生,可能有点强人所难了。但是,我们不仅有 vpulse,更有适用于此处的 vsource。

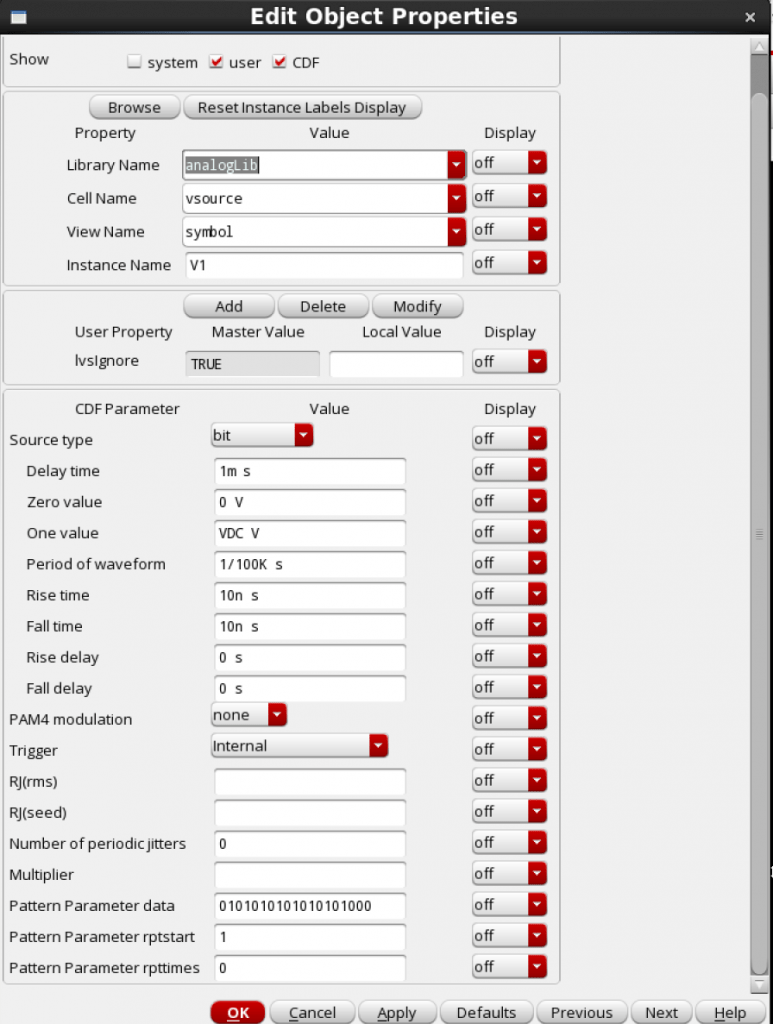

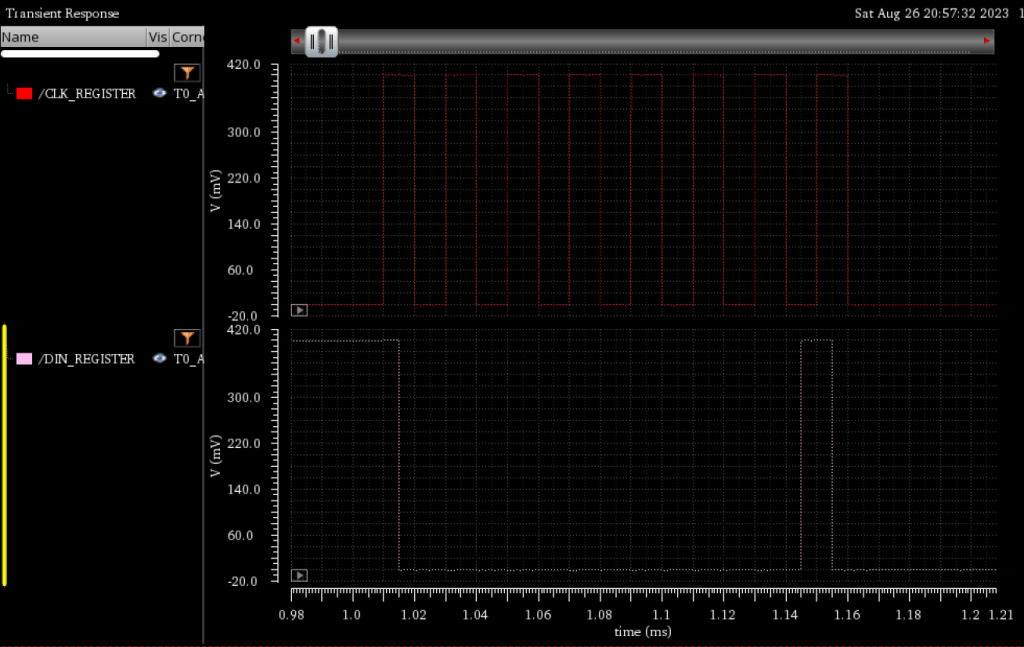

假设此时,我们需要按照 50K 的时钟速度,产生 8 个周期的时钟信号,就可以按照上图所示的方式设置 vsource,使其按照需求产生 8 个周期,50K 时钟速度的时钟信号,即 “1010101010101010”。单码字的持续时间为 1/100K s,则一个时钟周期的时间为 1/50K s。

结果十分明了,vsource 按照我们指定的时钟速度产生了 8 个时钟周期的时钟信号,且没有更多的动作。

实例2 – 产生 8 个 bit 的数据

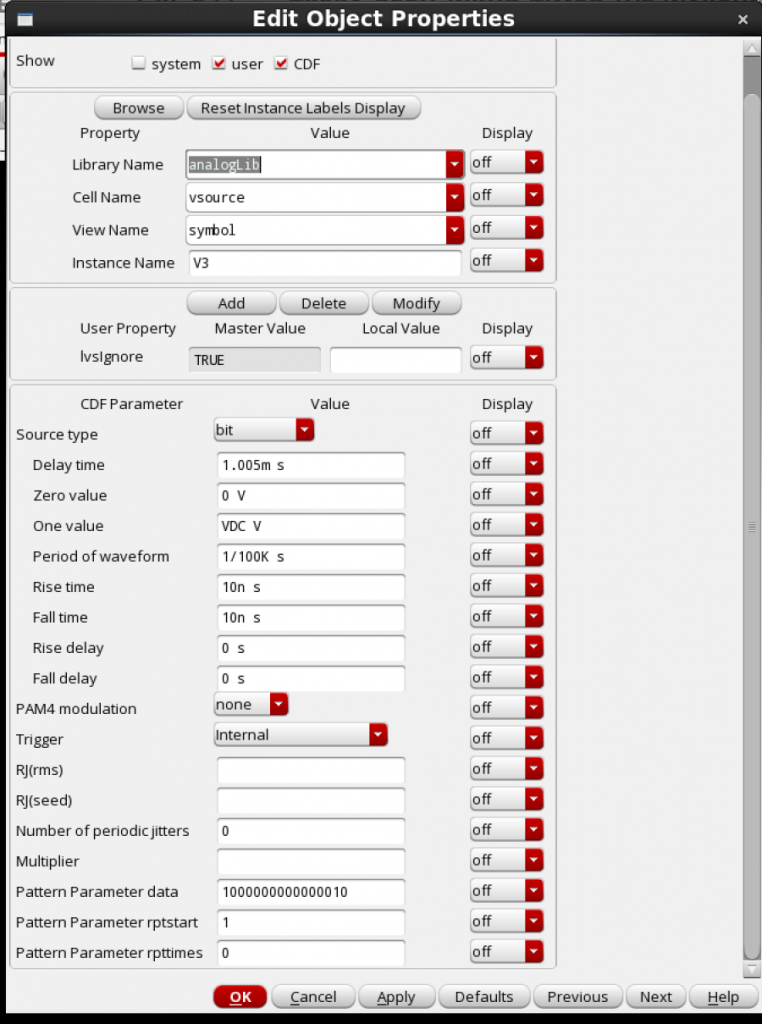

时钟信号有了,现在我们想要向数据输入处传入数据 0x81。这个需求同样可以通过 vsource 实现。

按照图示设置 vsource 的属性。为了保证时钟沿到来时数据的稳定,在该 vsource 处额外添加了半个周期的延时。

由于设置的数据频率与时钟频率相同,故 2 个数据的持续时间为一个时钟周期,0x81 的最高、最低位都为 1,因此设置的数据为 “1000000000000010”。末尾的0是为了让数据输入线在数据传输结束后保持低电平。

数据在时钟的上升沿被采样,MSB First,传入的数据值为 0x81。